下载美图秀秀2012-系统重装是什么意思

2023年4月6日发(作者:下载高速浏览器)

26

电罄与匣用

文章编号:1002—8692(2007)12—0026—02

一种AVS高清视频解码器的设计

郑 思,朱兰娟,刘佩林

(上海交通大学电子信息与电气工程学院,上海200240)

・实用设计・

【摘 要1提出了一种在150 MHz工作频率下实现AVS高清视频解码器的设计方案,对性能要求进行了分析,指出了解码器设计

需要解决的问题,给出了整体设计架构。对各关键环节的优化提出了设计方案,并在FPGA上验证该解码器。

【关键词】AVS标准;高清;解码器

【中图分类号】TN919.81 【文献标识码】A

Design of an AVS HD-video Decoder

ZHENG Si,ZHU l ̄.--juan,LIU Pei—lin

(School of Electronic Information and Electrical Engineering,Shanghai Jiaotong University,Shanghai 200240,China)

【Abstract】This paper proposes an architecture for AVS h J gh definition decoder with the operating frequency of 150 MHz.Based

O11 the analysis of performance required the paper points out the bottlenecks that should be solved and gives the overall design

.

Then the paper provides solutions for the optimization of key modules and validates the decoder on FPGA

.

【Key words】AVS;high definition;decoder

1 引言

AVS是我国自主开发的数字音视频编解码技术标

准,在编码效率和实现复杂度上取得了很好的平衡。高清

视频解码数据量大,计算复杂,对解码器性能要求极高,

同时,为降低解码器的功耗及资源消耗,要求在相对较低

的频率下,以较小的硬件代价实现设计要求[11。

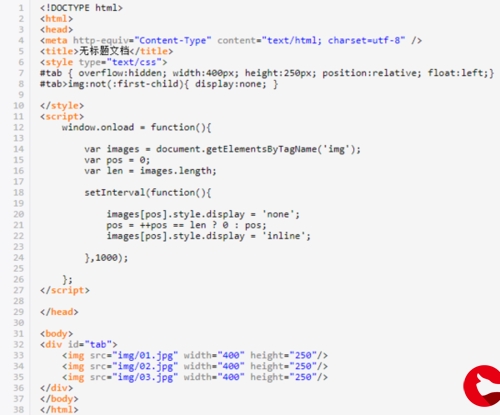

2 性能分析与整体设计

笔者设计的解码器能在150 MHz下,实时解码30 、

分辨力为1 920xl 080的高清码流;支持4:2:0,4:2:2格式,

支持逐行视频序列和隔行视频序列,全面支持帧内预测、

帧间预测及双向预测,最多同时使用2个参考帧;视频输

出支持CCIR656,601标准。将该解码器设计为一个AMBA

从设备,方便与外部设备进行数据交互,可移植性高。

解码器需解决的主要问题是提高解码速度和降低对

外存储器访问的带宽。为提高解码速度,节约资源,必须

设计一套高效的流水机制。在150 MHz频率下,平均每

个宏块解码占用周期数上限c:T 一612.7,

也就是说,在进行宏块级流水划分时,必须保证耗时最大

的一级解码1个B帧宏块所占周期数应低于612,更理

想的情况是低于600,以留有一定裕量。帧间预测包括计

算当前宏块的MV、进行像素插值、取参考像素点等工

作,因此,这一级是宏块级流水的瓶颈所在。

AVS需存储1帧当前显示帧,1帧当前解码帧和2

帧参考帧。对于4:2:2格式的码流,每帧所需空间为1 920x

1 080x2—4 Mbyte,共需16 Mbyte的存储空间,另外,每

电视接球 i 7年第3 卷第 鬲 6

个8x8块有1-2个22 bit的MV,需6 byte的存储空间,因

此存储MV共需 一200 Kbyte,外存储器

需选择为32 Mbyte。为节省芯片引脚,应选用DDR而不

是SDRAM。最坏情况下对外存储器的总带宽请求为

矍 田 设内存接口单元

广_h———

竺竺竺 竺竺竺 一._

(MIU)管理的效l1 .垒 呈垒 ! !堡旦 } f ^ f

}章—ea ̄erbit DDR 窜 32 存储l l J

器所能达到的带{ 豳I

宽为(假设DDR f臣 臣 臣 习 I J

工作于133 MHz){厂 ]— — l

133x32x2+8x60%f=二二二二 J 』=二 I

一638 Mbyt。,可 , —— —^l I

满足要求。解码器厂

整体设计如图1 图1 系统架构

所示。

3 解码器采用的关键技术

3.1高效分级流水线机制

在典型的流水划分中,全宏块级流水能达到最快的

解码速率,但各个流水级间的缓存需求巨大。全块级流水

虽能最大限度地降低缓存消耗,却由于各级流水对变长

解码模块的依赖而导致等待严重,降低了解码速率[引。本

解码器采用分级流水方式,如图2所示。宏块级流水第1

级由变长解码(VLD)、反变换反量化(IQIT)及帧内预测

(Intra)组成,帧间预测(Inter)为第2级,第3级是块效应

维普资讯

滤波(Deblock)。变长解码为块级流水的第1级,反变换

反量化与帧内预测为第2级。流水线级间以乒乓RAM

作为数据交换的载体,设计一个流水控制模块来调度各

模块间的流水切换。针对一些在后续模块使用的头信息,

在VLD模块解码完成后放人FIFO中,以较小的存储空

间代价换来较快的流水切换。变长码解码模块比反量化

反变换模块、帧内预测模块、帧间预测模块提前处理1个

宏块,比去块效应滤波模块提前处理2个宏块,近似达到

了理想流水线时序的要求。

VLD

IQIT

Intra

Inter

Deblock

HeadI BlkOl Blk1 I Blk2l Blk3l Blk4l Blk5

\ I BlkOI Blk1 I Blk2l Blk3I Blk4

\ l BlkOl Blk1 l Blk2I Blk3l Blk4

MB1 l MB2 l MB3

MB1 MB2}MB3

MB1 I MB2 l MB3 l

J MB1 I MB2 I MB3

l MB1 l MB2 I MB3

图2分级流水线

3.2分任务调度的内存接口单元(MIU)

视频解码过程中,需频繁地将数据写入和读出外部

存储器,访问DDR SDRAM时,需先激活要访问的存储

块,并锁存行地址,才能发读写命令。各个存储块间互相

独立,每个存储块只能有1行打开,要打开新的行必须关

闭原来的行。如果连续2个请求在同一存储块的不同行,

则不得不执行“关闭一激活一读取”的操作。同时,DDR

SDRAM有多个固定的时间参数,规定了命令之间必需的

时间间隔,而且,每一行都必须在一定时间间隔内刷新1

次。为解决上述问题,本文采取以下措施:

1)进行合理的地址映射,使得连续访问的数据尽量

存于同一行中。如图3所示,以8个像素点(共64 bit)作

为存取基本单元,将整个图像划分为若干个宽16AU、高

64的矩形,每个矩形映射到4个存储块上,每个存储块

图3 图像到DDR地址映射的

基本矩形

有256列(每列64 bit),

这样就把1个8AU ̄32

的块存储到1个存储块

上的一行中,相邻3块

存储在不同存储块中,

很大程度上减少了“关

闭一激活一读取”的操作。

2)将每个任务划分

为多个子任务,将处于相同存储块且不跨行的多个读写请

求划分为相同的子任务。将相同的子任务一起执行,避免

了频繁的跨存储块、跨行读写,以减少“关闭一激活”操

作。码流测试表明,MIU的时间利用率超过70%,满足

580 Mbyte/s的最坏带宽请求。

Cj-.(.川 thelr applieatio,s

3.3插值像素预取机制

在带宽请求中,运动补偿模块占主要部分,约

390 Mbyte/st2],引入预取机制可进一步降低带宽请求,减

小MIU的压力。文献[2】的统计结果表明,1个宏块的后3

个8x8块所需插值的很多像素点落在第1块的参考像素

周围,如果在读人第1块的同时顺带读人周围的像素点,

可减少再次访问外存储器的概率。但是,预取面积并非越

大越好,必须综合考虑命中率、资源消耗、实现复杂度等

因素。通过对25个码流的统计表明,在将预取面积选定

为块1的参考范围并横

向、纵向延伸8个像素

(见图4)时,可在效率和

资源消耗上取得平衡。亮

度带宽减少21.0%,色度

带宽减少27.8%,平均后

整个运动补偿带宽可以

减少约23%。采用预取机

制后,最坏情况下存储器

接口的带宽总和减少到

490 Mbyte/s。

图4预取区域

3.4可变流水级数的插值模块

在解码30 f/s、分辨力为1 920x1 080的高清码流

时,为保证视频播放的实时性,最坏情况下每秒需对

l 944 000个8x8的亮度块进行插值操作。为此,笔者设

计了一种级数可变的流水线结构,针对不同目标位置的

插值需要,自动选择5~8级流水线,执行包括输入数据延

迟、行方向滤波、列方向滤波、J点滤波、数据整理、1/4像

素滤波、输出通路选择和限幅等操作。该方法使得数据的

输入、处理和输出同时执行,避免了空闲等待、数据转置

和存放中间变量的开销,在提高运算速度的同时减少了

硬件资源的占用。使用该方法实现插值器,能有效控制芯

片面积和系统时钟频率凹。

3.5资源复用的反变换,反量化/反扫描

IQIT模块需对像素块中每个系数逐个做二维反变

换,为节约资源,反变换/反量化模块将二维变换分拆成2

个一维变换,重复利用同一个一维变换核,先对像素块每

行做一维反变换,再对其结果的每列做一维反变换。再将

转置寄存器堆作为共用存储器阵列,并行处理游程解码、

反扫描、反量化,将反扫描、反量化和反变换融合在一个

流水线处理单元中,以节省存储空间,加快处理速度[51。

4 仿真与FPGA验证结果

该解码器用Verilog HDL语言实现,使用Synplify和

Ise作为综合与布局布线工具,经Xilinx Virtex4 XC4VL)(80

(下转第30页)

N0.12 Vo1.31 2007(Sum No.309}、VII)B}聃脯壬 Il№ 27

维普资讯

[: 重量复癣 … …一

换过程实现,此时组逻辑左移位指令PSLLW需要变成组

算术右移位指令PSRAW。

3 实验测试

测试使用QCIF的Salesman,Mobile等视频序列来进

行,其中,Mobi1e序列为物体的剧烈运动,Salesman为物

体缓慢的移动。

表1,表2分别列出了不同视频序列在代码优化后,

利用SSE2对AVS—M编码参考软件WM3.0进行优化后

的编码结果。从实验结果可见,对于不同类型的序列,其

编码效率都有很大的提高。表3显示了优化前后的编码

速度差异。

表1优化后Mobile序列的编码数据

表2优化后Salesman序列的编码数据

从以上结果可以看出,经过SSE2优化及部分C代

码的调整,程序的运行效率有了极大的提高。

4 小结 表3 优化前后的编码速度比较

从SIMD技术的

原理出发,对SSE2

指令集作了简单介

绍。在此基础上提出

了对于编码器中运动搜索与估计的SAD计算,亚像素插

值,整型DCT变化与反变化等模块的SSE2优化。实验证

明,优化取得了较好的效果,编码器的运行速度有了很大

的提高

参考文献

[1]张颖,王兴国,刘济林.基于单指令多数据流技术的视频信息处理

优化[JJ.电视技术,2003,(11):40—43.

[2]李蕊,陈浩,姜昱明.SSE在多媒体数据处理中的应用【JJ.计算机应

用,2002,22(7):99—103.

[3】Intel corporation.IA一32 Intel architecture soflware developer S

manual,volume l:basic architecture[EB/OL]. ̄2oo5一l2-311.fttp://

download.inte1.com/design/Pentium4/manuals/253665 17.pdf.

[4]Inte1.Block-matching in motion estimation algorithms using streaming

SIMD extension 2(SSE2)version 2.0[EB/OL].[2000-07-31].http://

cedar.inte1.com/media/pdf/appnotes/sse2/w

—me

—

alg.pdL

【5]Inte1.Using streaming SIMD extension 2(SSE2)to implement an

inverse discrete cosine transform version 2,0[EB/OL]. [2004-12—08].

http://www.inte1.com/cd/ids/developer/asmo-na/eng/dc/code/optimization/

193014.htm.

作者简介:

钱金法(1962一),副教授.研究方向为信号与信息处理;

赵力(1960-).教授,博士生导师.研究方向为信号与信息处理。

责任编辑:许盈 收稿日期:2o07—10--19

(上接第27页)

表l 各模块的资源占用情况 型FPGA验证,在54

MHz频率上实现了

实时SD码流的播放,

在74.5 MHz以15£/s

的速率通过了高清码

流的播放验证。各模

块的逻辑占用情况如

表1所示。

总体来说,该解

码器能在较低频率

和较少的资源占用条件下实现了AVS高清视频播放,具

有很好的可移植性,可广泛应用于数字电视、机顶盒、

IPTV、移动视频终端和互联网流媒体等方面。

参考文献

[1]中华人民共和国国家质量监督检验检疫总局,中国国家标准化管

电视技球12007 ̄31卷第12期(总第309期l

理委员会.GB/T20090.2—2006信息技术先进音视频编码第2部分:

视频[S].北京:中国标准出版社,2006.

【2]陆泳,张文军,刘佩林.多标准视频硬件解码器的存储器地址映射

方法【J].电视技术,2006(12):39-42.

[3]孙楠,刘佩林.用于AVS视频解码器的高效分级流水线机制[JJ.

电视技术,2006(1 1):35—37.

[4]赵策,刘佩林.AVS游程解码、反扫描、反量化和反变换优化设计[JJ.

信息技术,2007(2):54—57.

[5】ZHOU Dajiang,LIU Peilin.A hardware—efficient dual—standard

VLSI architecture for MC interpolation in AVS and H.264[J1. IEEE

ISCAS 2007.2oo7f5):2910-2913.

作者简介:

郑思(1982-),硕士生,主研多媒体芯片设计;

朱兰娟.女,副教授,主要研究方向为嵌入式系统设计;

刘佩林.女.教授。主要研究方向为多媒体芯片设计。

责任编辑:任健男 收稿日期:2007-09—25

维普资讯

更多推荐

高清视频解码器

发布评论